# CBCS SCHEME

| USN |  |  |  | <br>n * |  | 15EC53 |

|-----|--|--|--|---------|--|--------|

|     |  |  |  |         |  |        |

# Fifth Semester B.E. Degree Examination, Jan./Feb. 2021 Verilog HDL

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

# Module-1

- Explain the design flow of VLSI IC circuit steps with a neat flow chart. (08 Marks)

- List the useful features of verilog HDL for hardware design. (05 Marks)

- Explain the importance of HDL compared to traditional schematic based design. (03Marks)

# OR

- Explain TOP-down methodology applying to design of 4 bit Ripple carry counter. (08 Marks) Explain the components of simulation.

(08 Marks)

Module-2

Explain any four datatypes in vertilog. Explain in brief the system task and compiler directives. (08 Marks) (08 Marks)

- Explain the concept of mapping of ports to external signals with one example. (08 Marks)

- Declare top level module stimulus. Define REG IN(4 bit) and CLK(1 bit) as reg register variables and REG - OUT (4 bit) as wire. Instantiate module shift-reg and call it sr1. Write hierarchical names for variables, REG - IN, CLK and REG - OUT. Also write hierarchical name for instance srl. (08 Marks)

# Module-3

- Write a design block and stimulus block for 4:1 MUX using gate level modeling. (08 Marks) 5

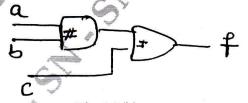

- Write a verilog code for function f = (ab + c) with specified delay and also draw neatly the simulated output waveform.(Ref. Fig.Q5(b)).

Fig.Q5(b)

(08 Marks)

### OR

- Explain relational, equality and bitwise operators in verilog with example. (06 Marks)

- Write data flow modeling for 4 bit FA with carry look ahead. (10 Marks)

# Module-4

- Describe multiway branching using case, case X, case Z with example. (09 Marks) 7

- Write Behavioral modeling for 4:1 MUX using case statement. (07 Marks)

15EC53

OR

8 a. Describe while, for, forever statements in verilog with syntax.

b. Write behavioral modeling for 4 bit counter program in verilog.

(09 Marks)

(07 Marks)

Module-5

9 a. Explain in brief the design process of using VHDL for design synthesis. (10 Marks)

b. Explain the EDA tool flow with neat diagram. (06 Marks)

OR

a. Discuss the scalar data types used in VHDL.

b. Write a note on attributes in VHDL.

(08 Marks)

(08 Marks)

2 of 2